- select language:

- KR

- EN

주메모리로서 DRAM 역활

CPU가 발전할수록 CPU와 Memory간 속도차가 커짐

CPU는 속도에 DRAM은 용량과 가격에 더 주안점을 두고 발전

캐시메모리 SRAM 사용은 CPU와 DRAM간의 속도차를 줄여주는 한 방법

캐시메모리 SRAM 역활과 Trade-off

하드디스크보다 훨씬 빠른 저장메체 SSD 등장

SSD중 PCIe 인터페이스를 사용하여 속도를 개선한 NVMe-SSD 등장

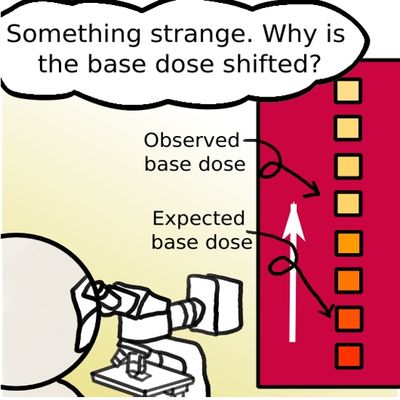

극단의 조건에서 SSD data 안정성

Please consider becoming a sponsor of my work

- Scroll to:

- Ep1

- Next

Reference

- Carlos , Carvalho. Universidade do Minho. “The Gap between Processor and Memory Speeds.”

- Zahran, M. New York University. Lecture 3: “The Memory System.”

- Onur , Mutlu, et al. Carnegie Mellon University. “The Main Memory System: Challenges and Opportunities.”

- Lee, Donghyuk, et al. Carnegie Mellon University. “Tiered-Latency DRAM: A Low Latency and Low Cost DRAM Architecture.”

- “Samsung NVMe SSD.”

- Pratt, Tom. Micron. “The Real World of Emerging Memories.”

Leave a Reply