Summary

저항변화를 이용하는 차세대메모리인 STT-MRAM/PCRAM/ReRAM가 개발되고 있는 가운데 DRAM은 새로운 3D power scaling 시대로 나아갈 희망을 갖는다.

- select language:

- KR

- EN

차세대메모리 Big3 : PCRAM, STT-MRAM, ReRAM

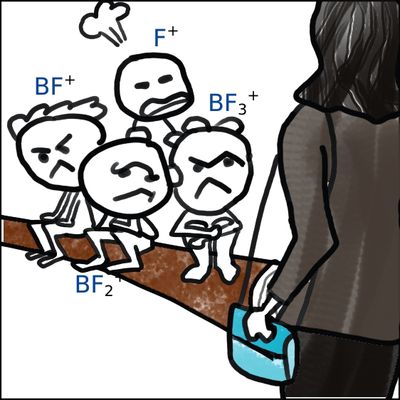

차세대메모리는 저항기반 비휘발성 메모리

*Short Channel Effect(단채널 효과): Effects occurred when the channel length of MOSTETs is the same order of magnitude as the depletion-layer widths of the source and drain junction

DRAM은 계속진화할 것

Moore’s Law는 3D power scaling으로 변신

Please consider becoming a sponsor of my work

Reference

- Ping Er-Xuan. AMAT. 3D Architecture and Interconnect for Emerging Memory Technologies. SPCC 2016.

- “How new Non Volatile Memories Are Enabling Disruptive Computing Architectures?”. Denis Dutoit, CEA-LETI. Flash memory summit, 2017.

- Hutcheson G.D. (2009) The Economic Implications of Moore’s Law. In: Huff H.R. (eds) Into the Nano Era. Springer Series in Materials Science, vol 106. Springer, Berlin, Heidelberg.

- “ITRS Reports.” International Technology Roadmap for Semiconductors, www.itrs2.net/itrs-reports.html.

- “Energy Aware Memory Technology and New Memory System Hierarchy” Frank Koch. Samsung Semiconductor Europe GmbH. 2013.

- “An Overview and Future Challenges of High Density DRAM for 20nm and Beyond.” Yoosang Hwang, et al. Samsung. SSDM 2012.

- “Memory Scaling: A Systems Architecture Perspective.” Onur Mutlu, Carnegie Mellon University. 2013.

Leave a Reply